本文内容基于 2025 秋季《计算机体系结构》双语班课程讲述,如有差错,欢迎指正

回顾#

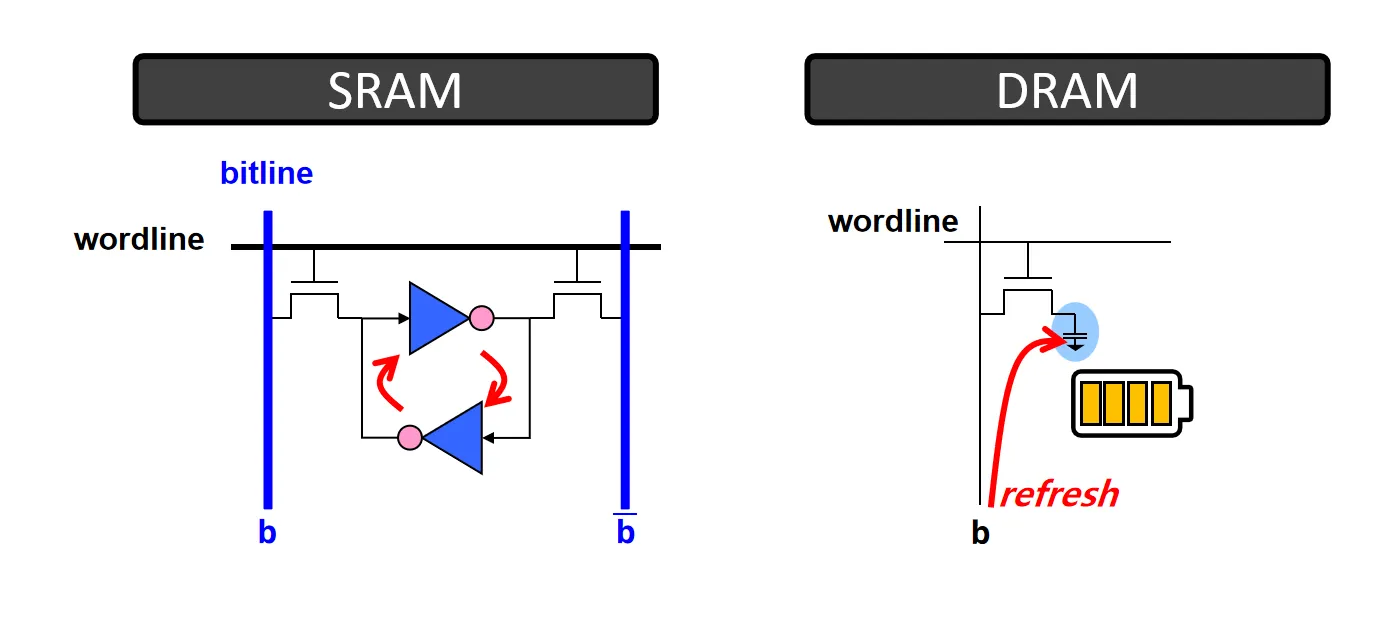

易失型储存只在有电力供应时保存数据,断电后数据丢失,比如 RAM

对于一些数据,我们希望它们在掉电后仍能保存,因此我们需要非易失型存储 (Non-Volatile Memory, NVM)

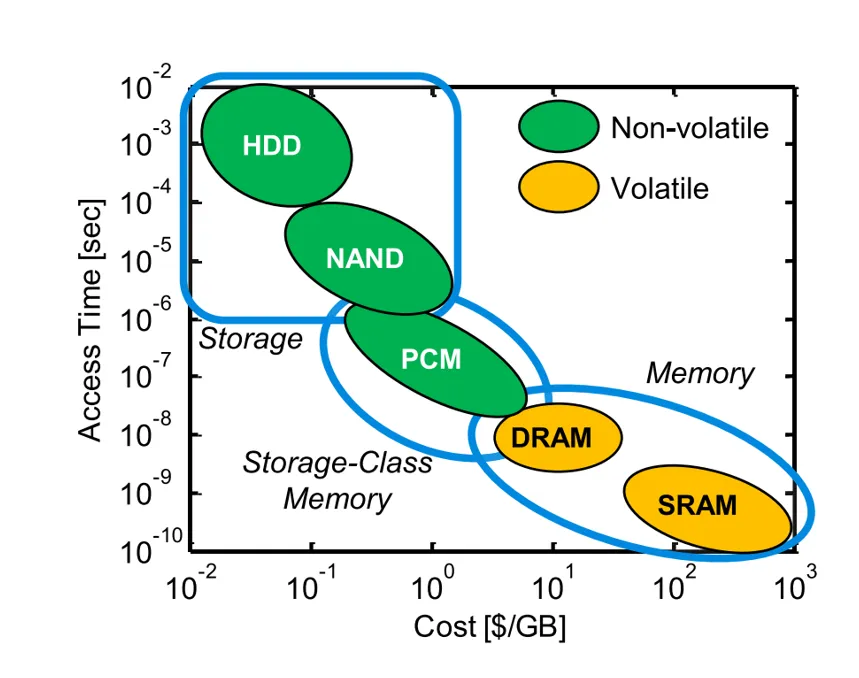

Semiconductor Memory Hierarchy

![]()

新兴 NVM (存储级内存 SCM):#

定位: NVM 也被称为存储级内存 (Storage-Class Memory, SCM) ,它填补了传统存储(如 HDD)与易失性内存(如 DRAM)之间的巨大性能鸿沟 。

新兴 NVM 技术(部分):

- FeRAM (Ferroelectric RAM, 铁电存储器)

- MRAM (Magneto-resistive memory, 磁阻存储器)

- PCM (Phase Change Memory, 相变存储器)

- Flash (闪存)

NVM Background#

硬件中逻辑上的 ‘0’ 和 ‘1’ 一般是由存储单元的电阻值来定义的,本文中认为电阻低代表逻辑’0’,电阻高代表逻辑’1’

- Program(Set) 操作:把逻辑’0’变成逻辑’1’

- Erase(Reset) 操作:把逻辑’1’变成逻辑’0’

如何区分数据?

电阻的高低只是个相对值,我们需要设定一个参考值 (Read Reference) 来区分 ‘0’ 和 ‘1’

实际设计时不会读电阻,而是给一个电压读取电流大小。

NVM Techniques#

本文介绍两种 NVM 技术的原理: Flash 和 PCM

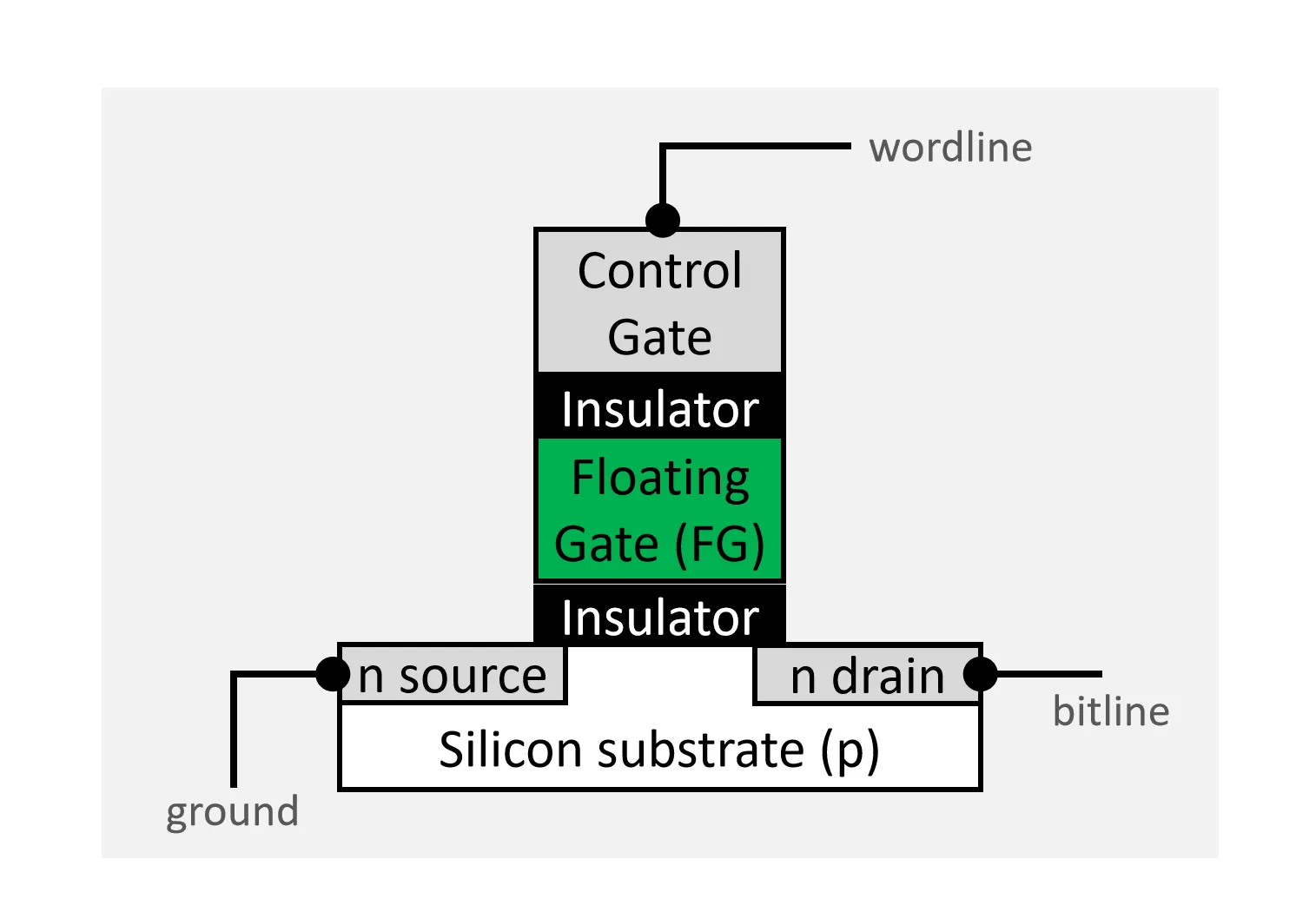

Flash#

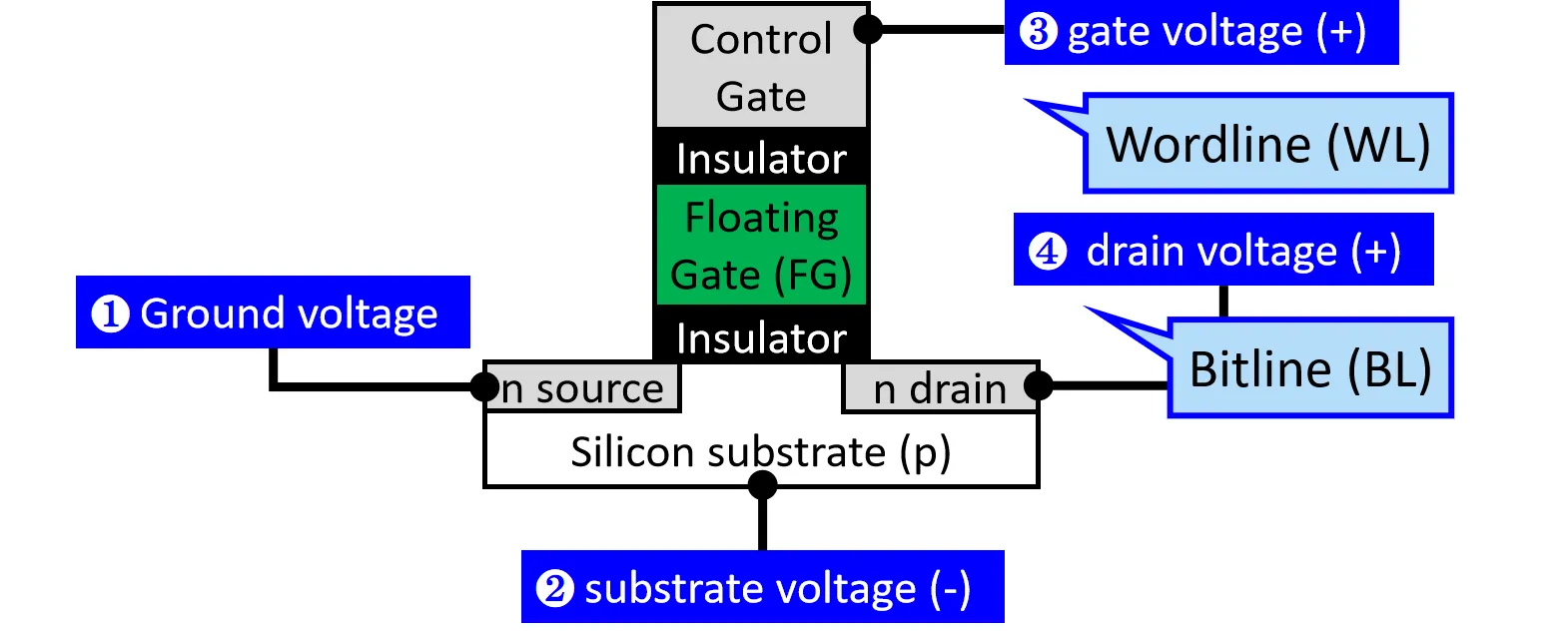

闪存的物理结构其实就是在三极管的结构基础上加了一个 Floating Gate 和两层 Insulator

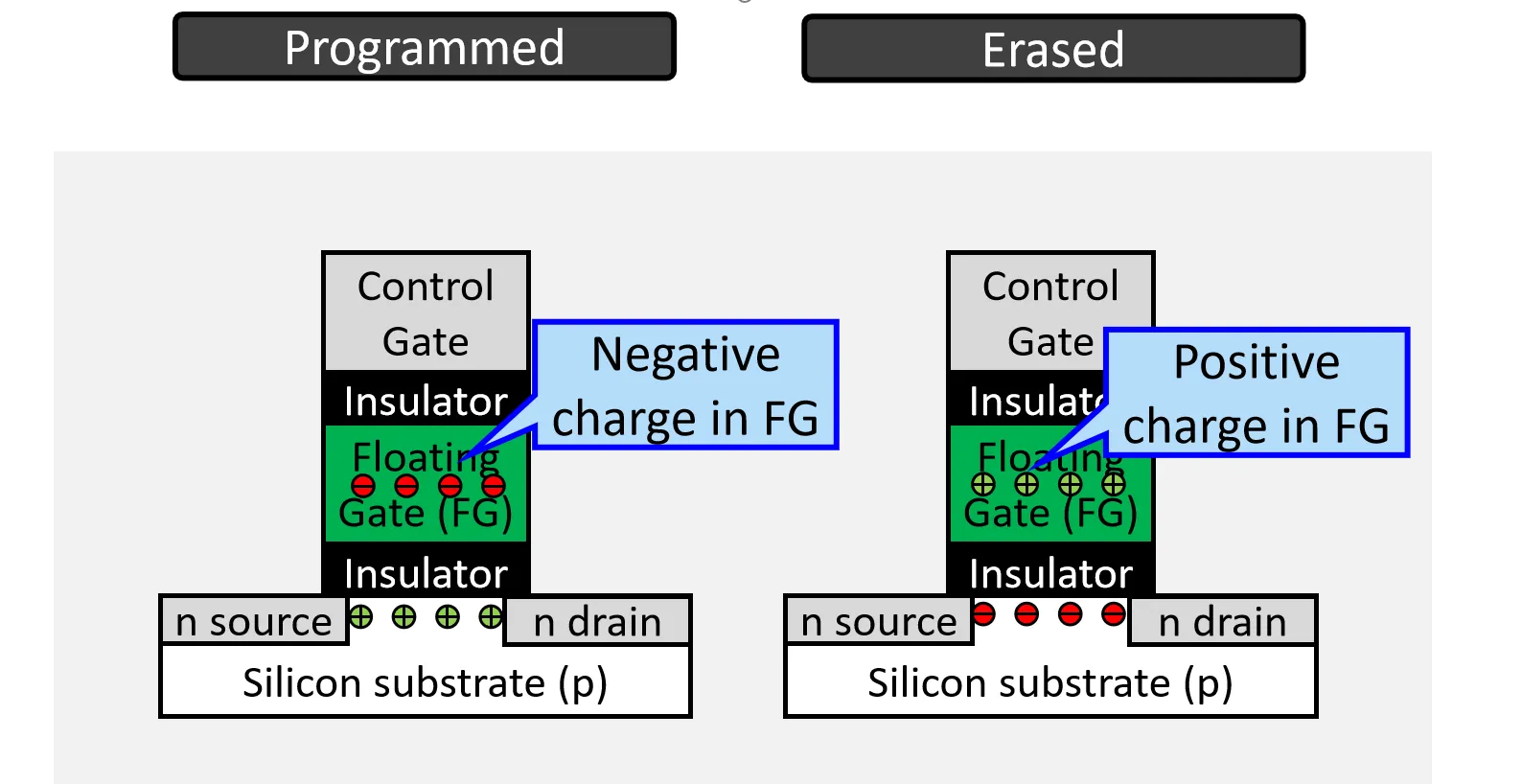

Floating Gate 可以存储电子, Insulator 的作用是隔离,电阻的大小与Floating Gate 上的电子数量有关

- Program 操作:在Control Gate上施加一个高电压(20V),下方的Insulator发生隧穿效应,substrate上的电子进入到Floating Gate上

当电压撤去后,由于Insulator的作用,电子被困在Floating Gate上,保存了电阻状态

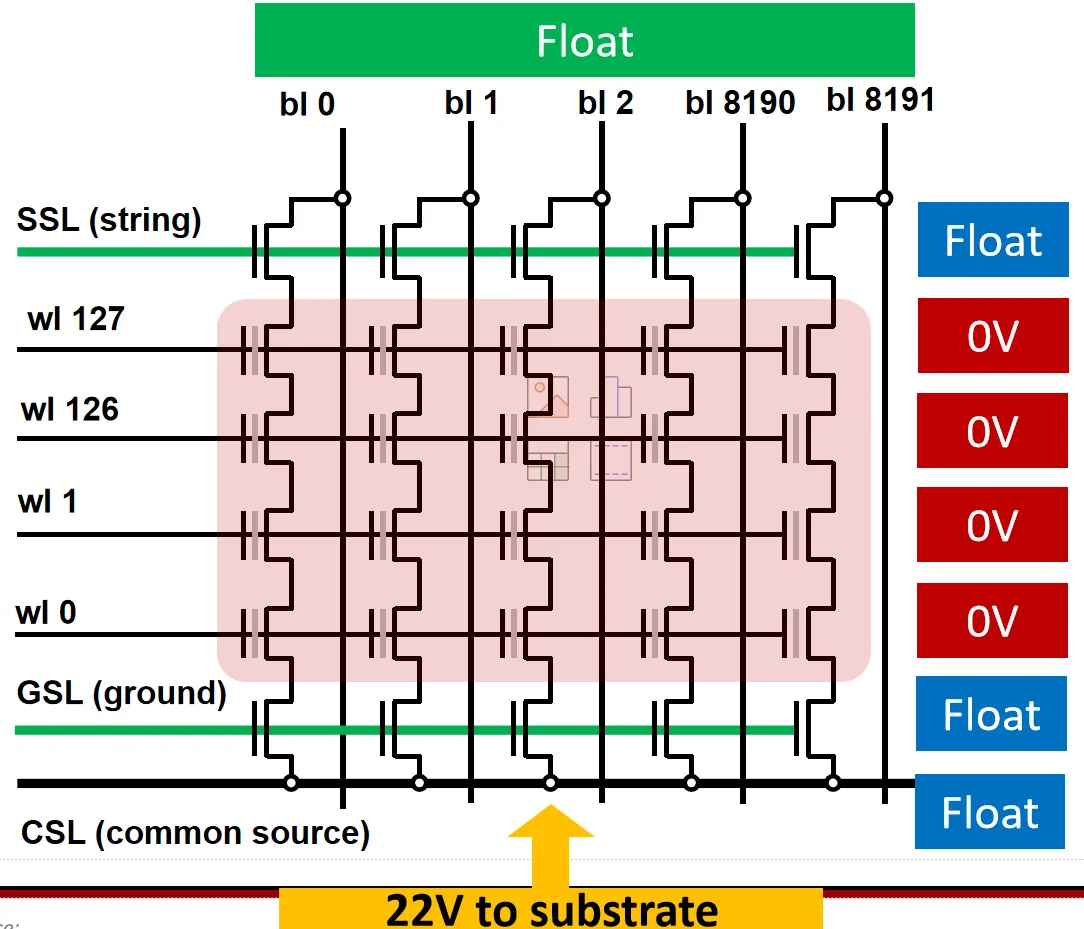

- Erase 操作:在Substrate上施加一个高电压(20V),Floating Gate上的电子被吸回到Substrate上

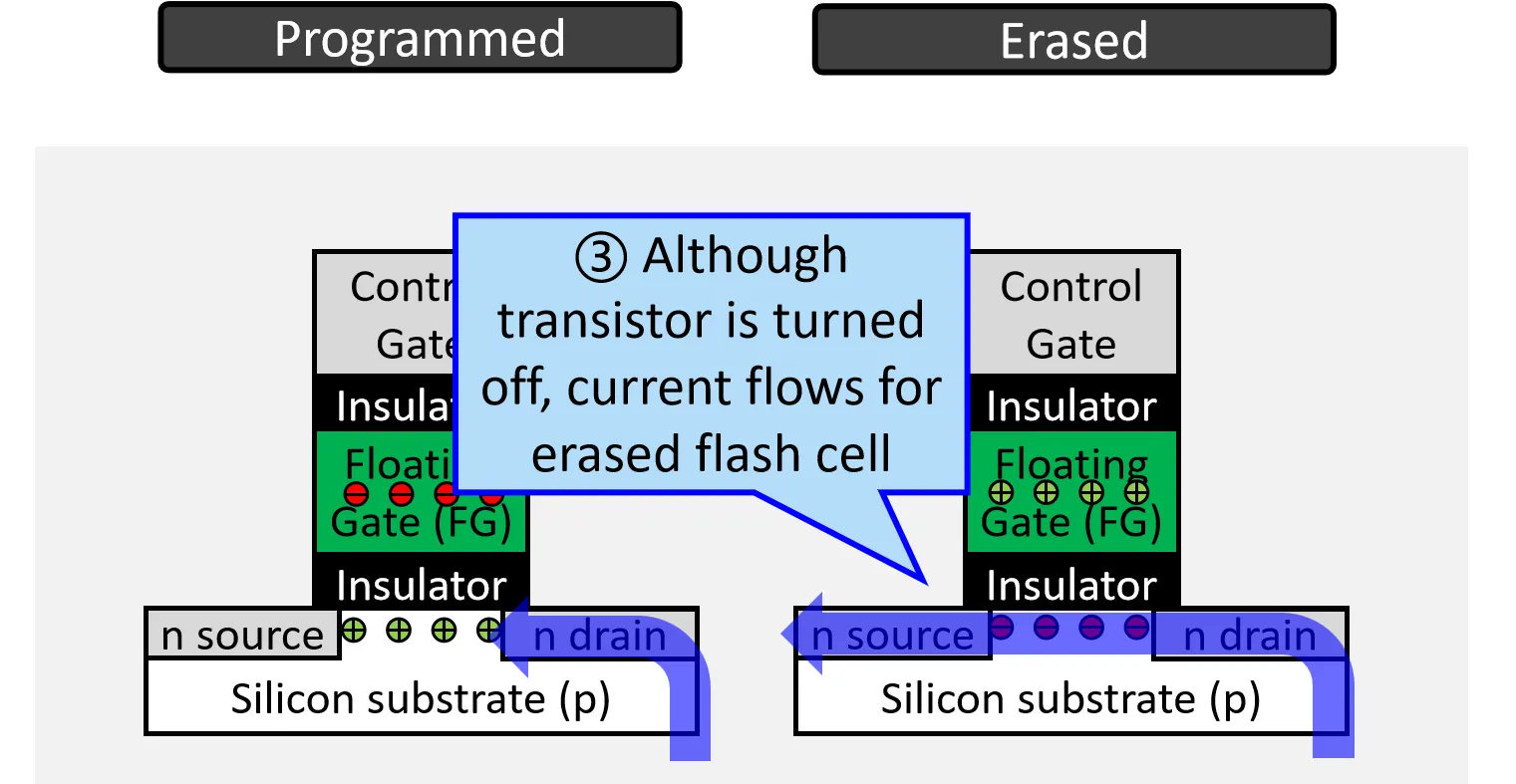

source 和 drain 之间的电阻状态由 Floating Gate 上的电子数量决定

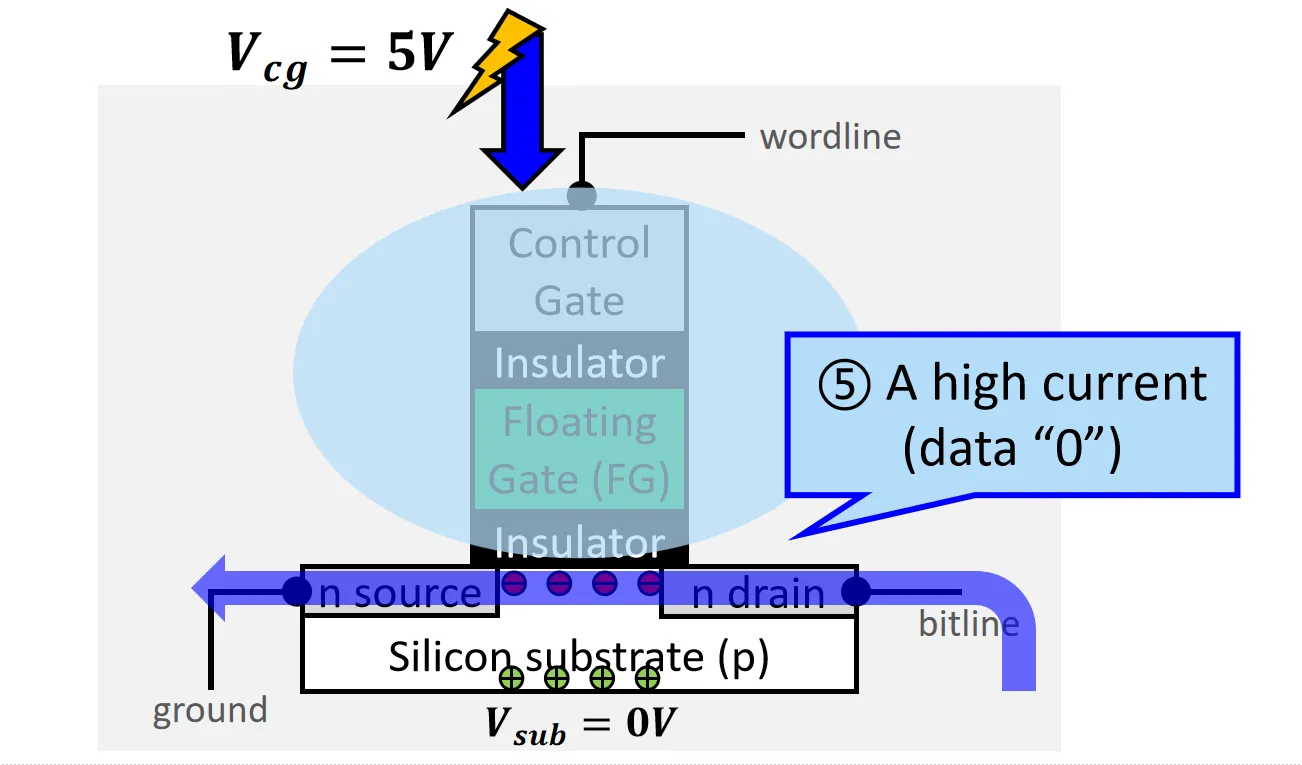

- Read 操作:关掉Control Gate(0V),在source和drain之间施加一个较低的电压(1V),根据流过的电流大小判断电阻状态

substrate上电子数量少,source和drain之间电流小,为逻辑’1’,反之为逻辑’0’

flash进行读操作时施加的电压低,写操作时施加的电压高,故读的功耗低;读操作只需测量电流,写操作需要注入电子,故写延迟远高于读延迟

- Vpass 读操作:在 Control Gate 上施加一个中等电压(5V),使得 Source和Drain之间电子可以流动,读出逻辑’0’

Vpass 的用处后续章节介绍

PCM#

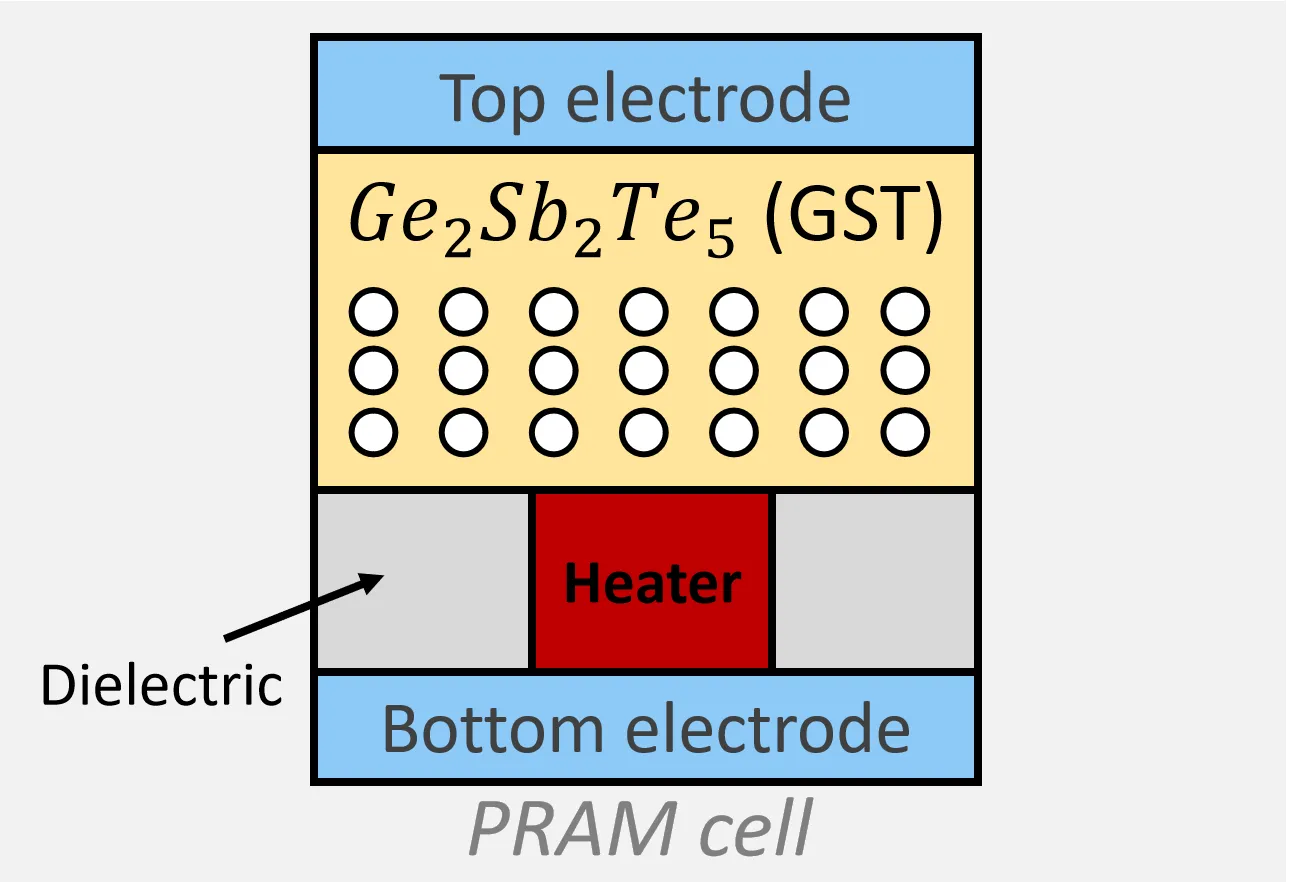

PCM的电阻状态由相变材料(: GST, Chalcogenide)的物理状态决定

通过加热使GST材料发生相变从而改变电阻

- 加热GST,材料变为无序的非晶态 (Amorphous),电阻高,定义为逻辑’0’

- 缓慢冷却GST,材料变为有序的晶态 (Crystalline),电阻低,定义为逻辑’1’

下面介绍如何通过加热实现相变

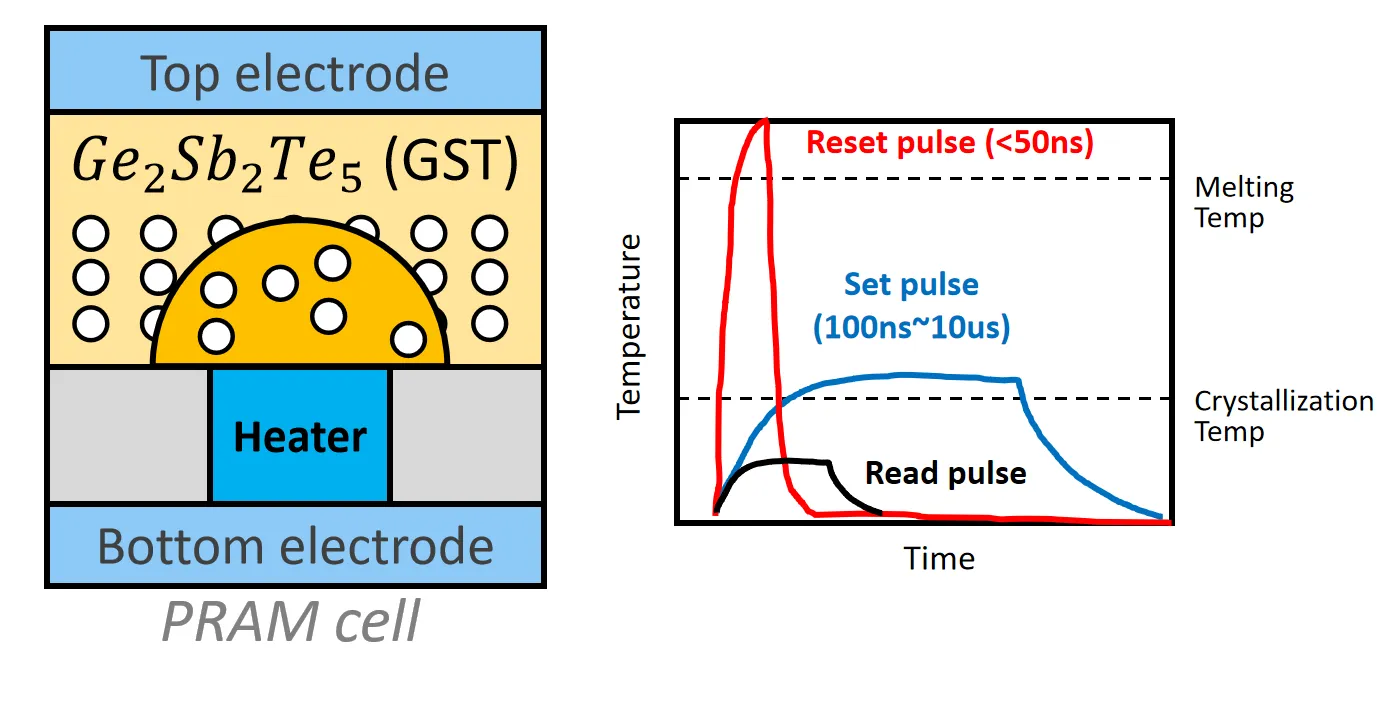

- Set(Program)操作:较长时间给加热器一个中等的电流(),GST慢慢融化并结晶

- Reset(Erase)操作:短时间给加热器一个较大的电流(),GST快速融化后迅速冷却成非晶态

- Read操作:给加热器一个较小的电流(),测量通过GST的电流大小判断电阻状态

NVM Array-level#

Flash#

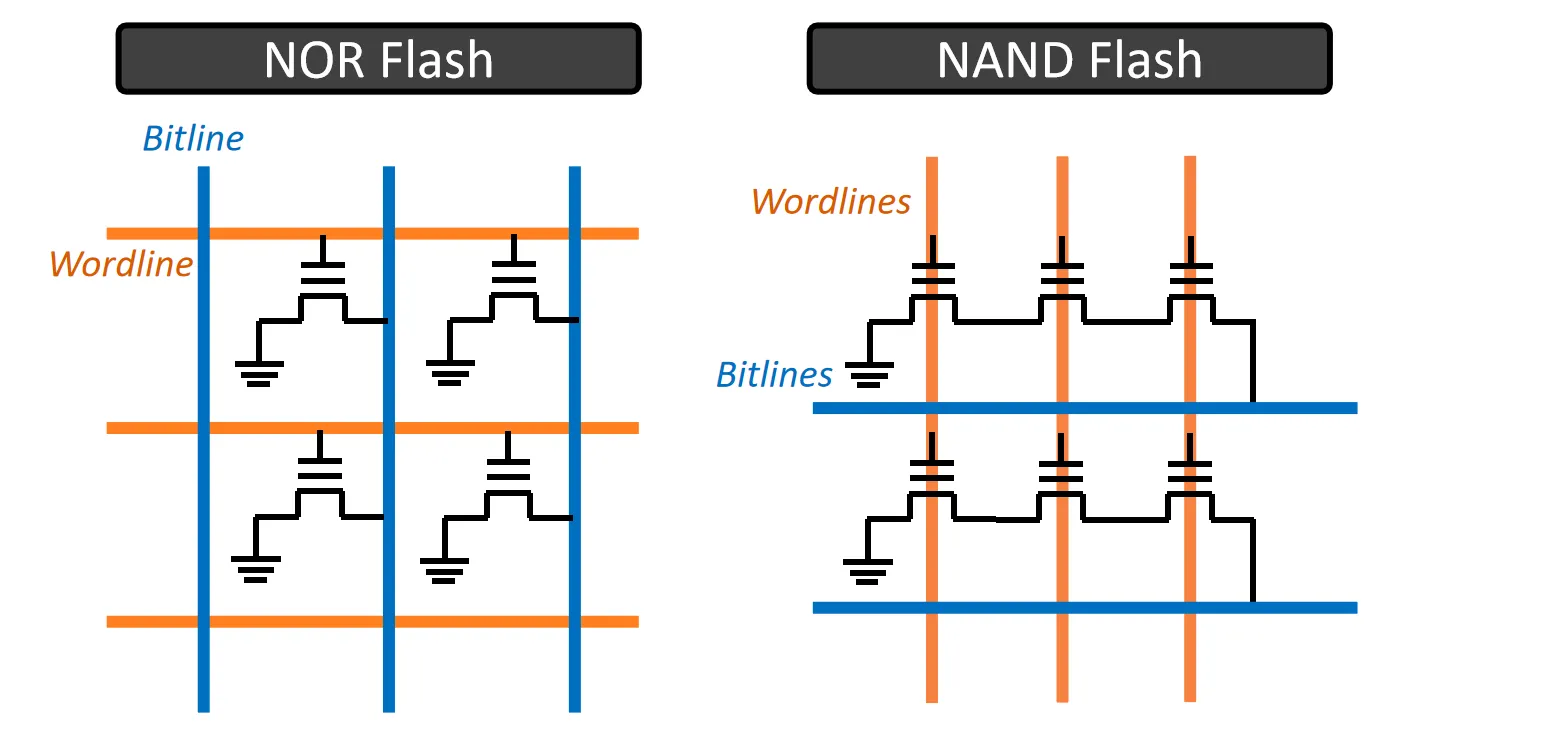

怎么接线把Flash cell之间相连:

- word line: 连接所有单元的Control Gate

- bit line: 连接所有单元的Drain

- source line: 接地

有了接线的方法,下面怎么将其组成存储阵列:根据bit lines sharing分为两类

两者比较:

- NAND Flash 少了很多 bit lines,存储密度更高

- NAND Flash 读取时需要把其他单元的Control Gate都拉到Vpass电压,保证source和drain之间的电子可以流动,才能读取所需单元,NOR Flash则不需要

- NAND Flash 的读写比NOR Flash 慢很多

- NAND Flash 一般用于存储数据,NOR Flash 一般用于存储执行的代码(NOR Flash和DRAM很像)

- NAND Flash 最小访问单位是 page (多个连续的 words),只有row address,而 NOR Flash 最小访问单位是 word,和 DRAM 一样

PCM#

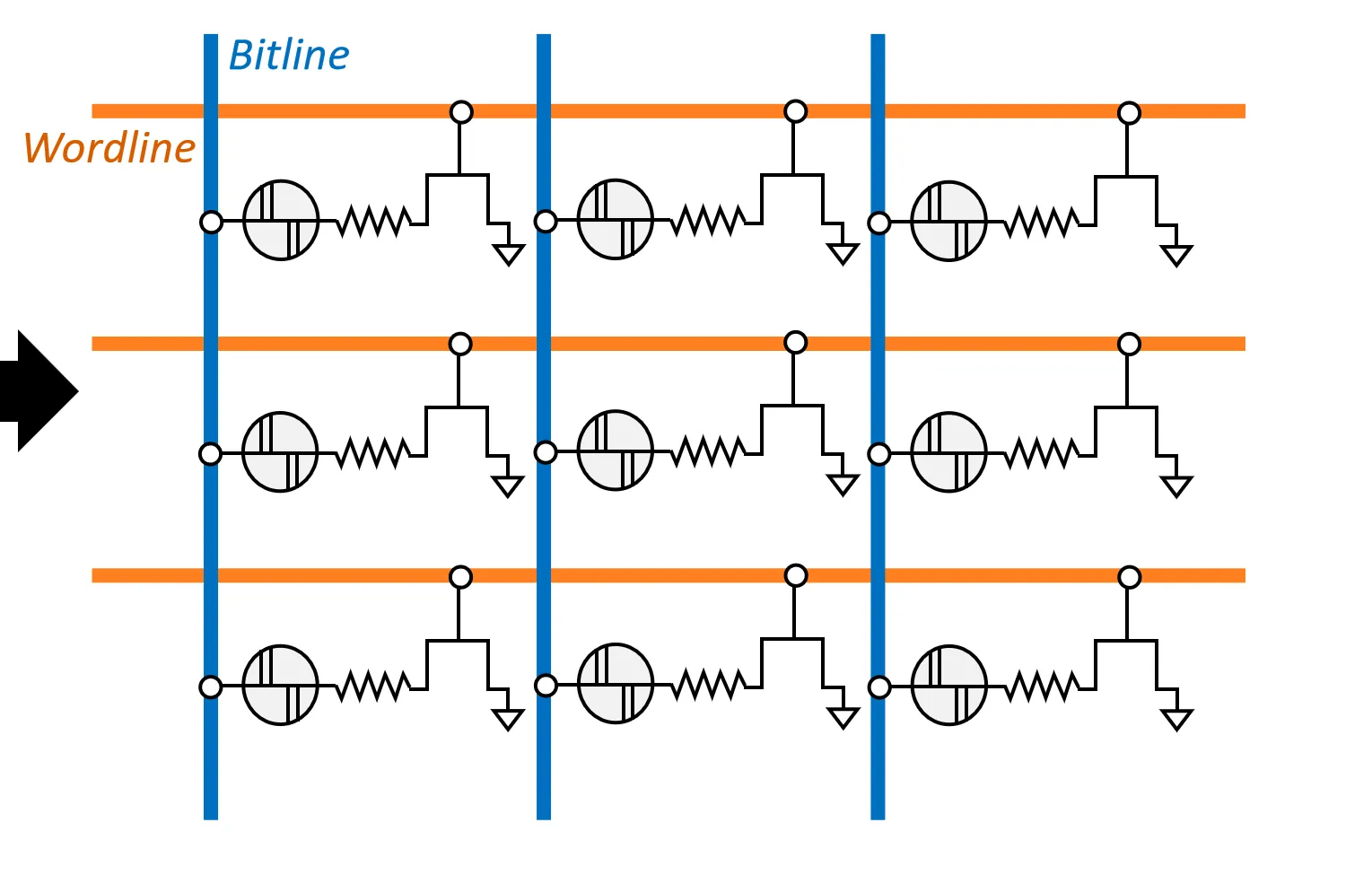

PCM 阵列与 DRAM 阵列类似

PCM 寻址也和 DRAM 相似:

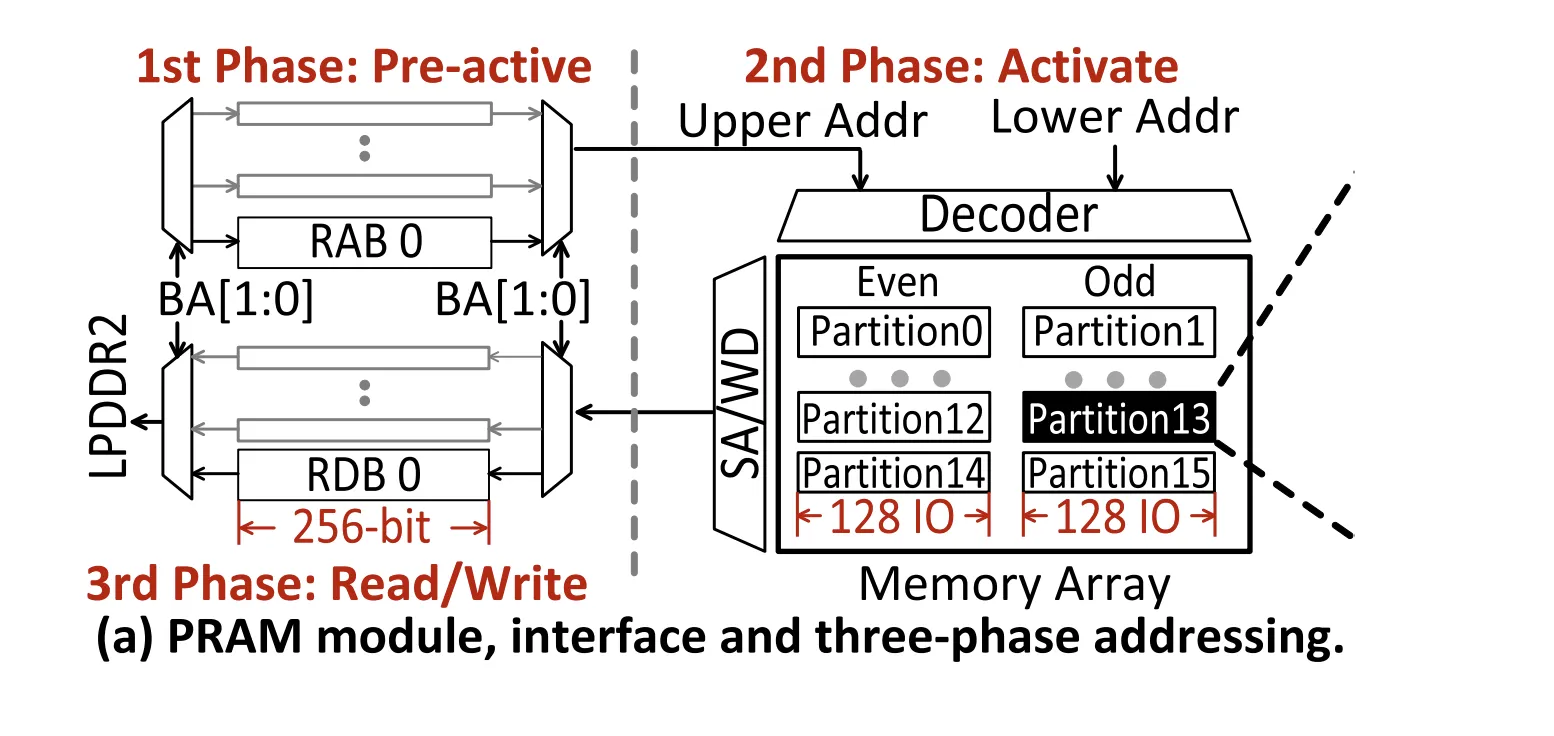

PCM进行读取操作有三个阶段

- Phase1:先发送Upper Address到RAB

- Phase2:再发送 Lower Address 和 Upper Address 共同进入 Decoder 寻址

- Phase3:把取出的行放到RDB后根据Column Address选择具体的单元进行读写

NVM w/ Bigger-Memory#

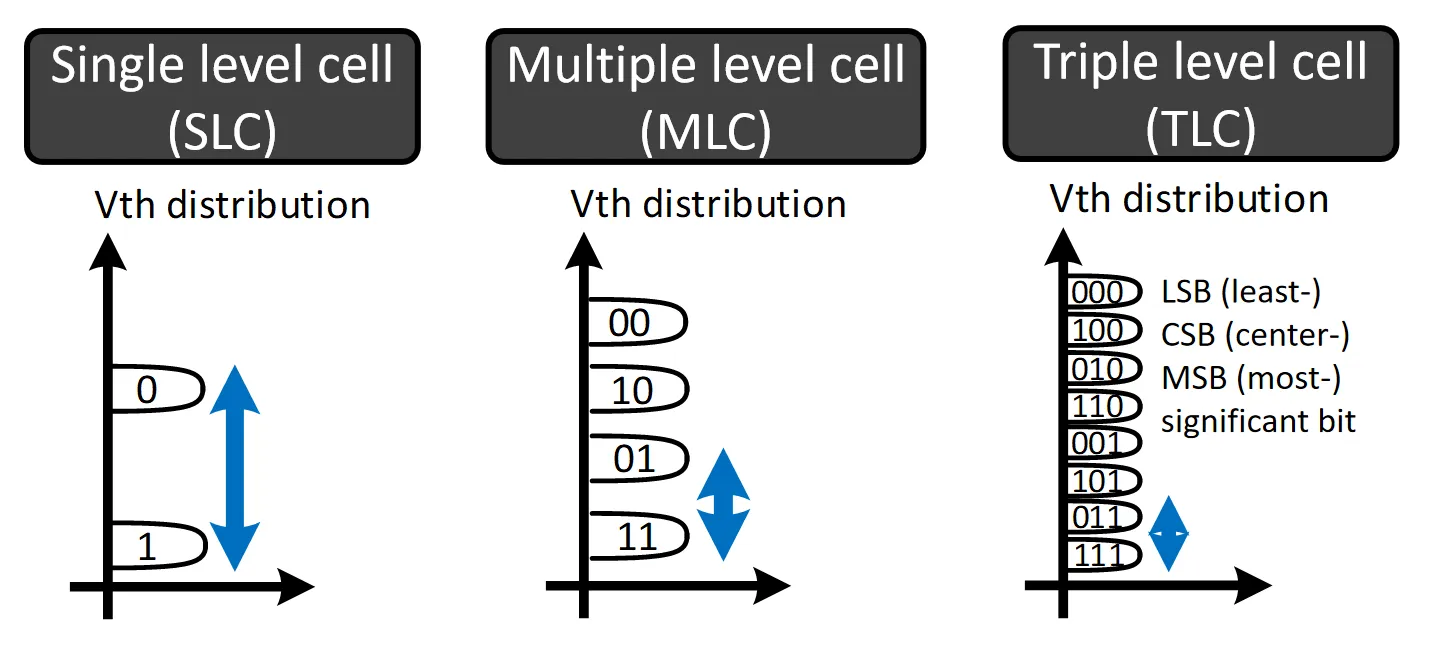

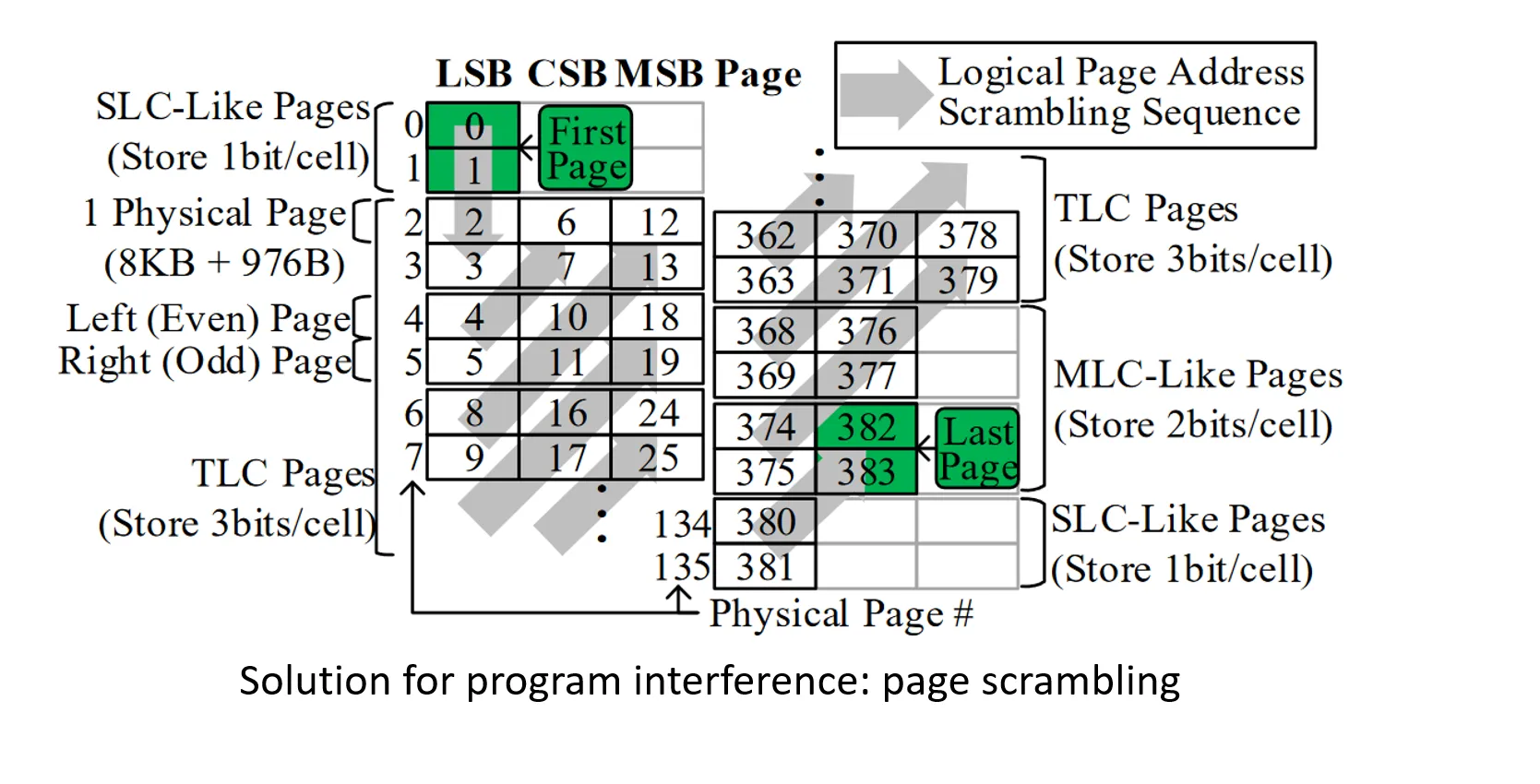

主要思想: Multi-level Cell (MLC)

对于flash和PCM来说,可以通过存储单元的不同电阻状态来表示更多的比特

对 TLC ,我们对其表示的每个bit进行命名以作一些额外区分

- MSB: Most Significant Bit (最高有效位)

- CSB: Center Significant Bit (中间有效位)

- LSB: Least Significant Bit (最低有效位)

这样虽然可以增加存储密度,但也带来一些问题:

- 状态之间的电阻差变小,出错概率变高,需要纠错

Flash#

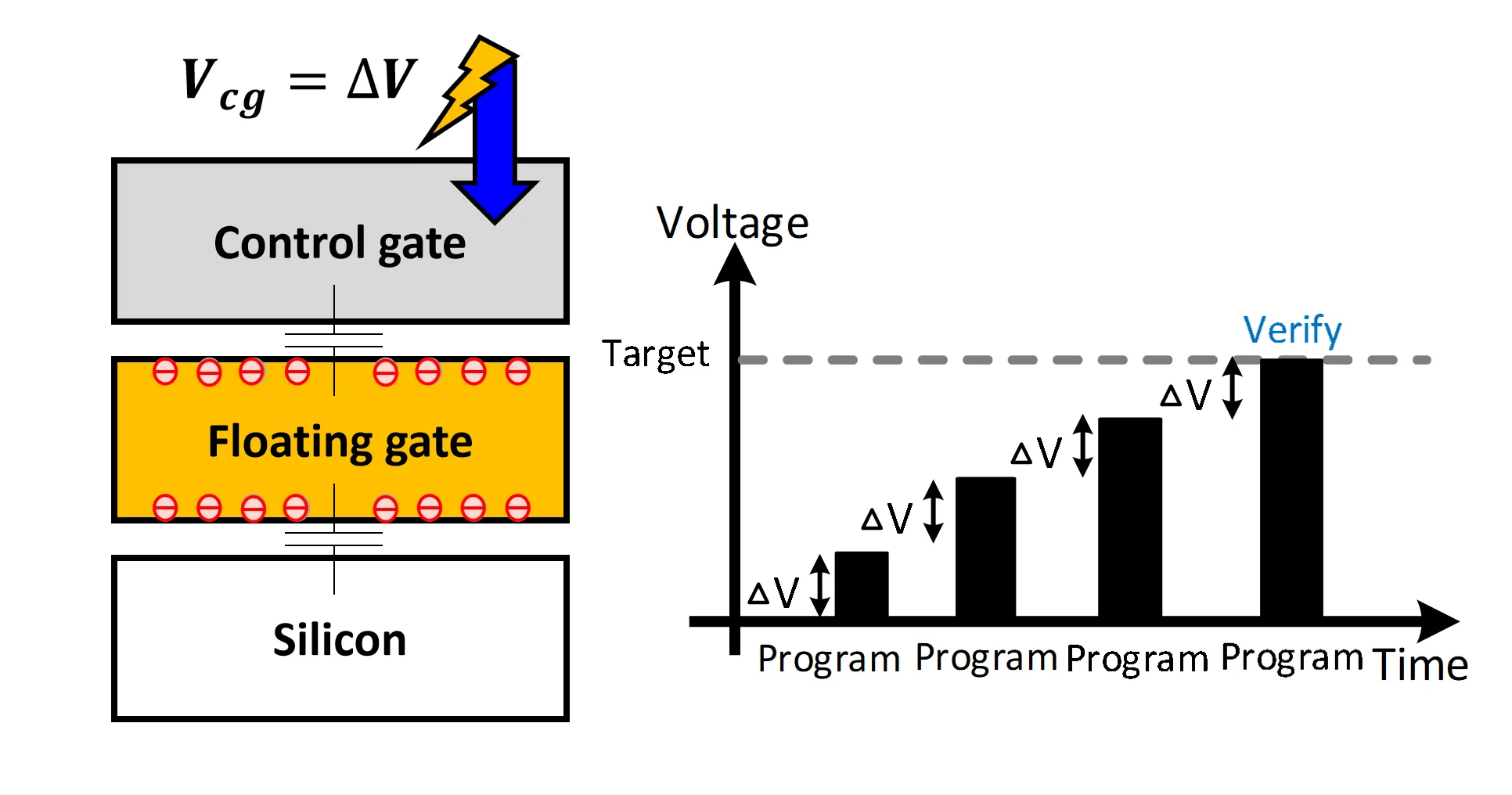

Flash中MLC的实现需要控制向FG中注入电子的数量,但肯定无法精确

原则:ISPP (Incremental Step Pulse Programming)

通过多次注入小量电子逐步接近目标电阻状态,每次写后读出当前电阻状态,判断是否达到目标状态,未达到则继续注入

但这种方式会显著增加写延迟:一次写会分为多次写和读,且不同位的延迟不同,MSB写延迟甚至比HDD还高

频繁的写操作还会加速NVM的磨损,影响寿命

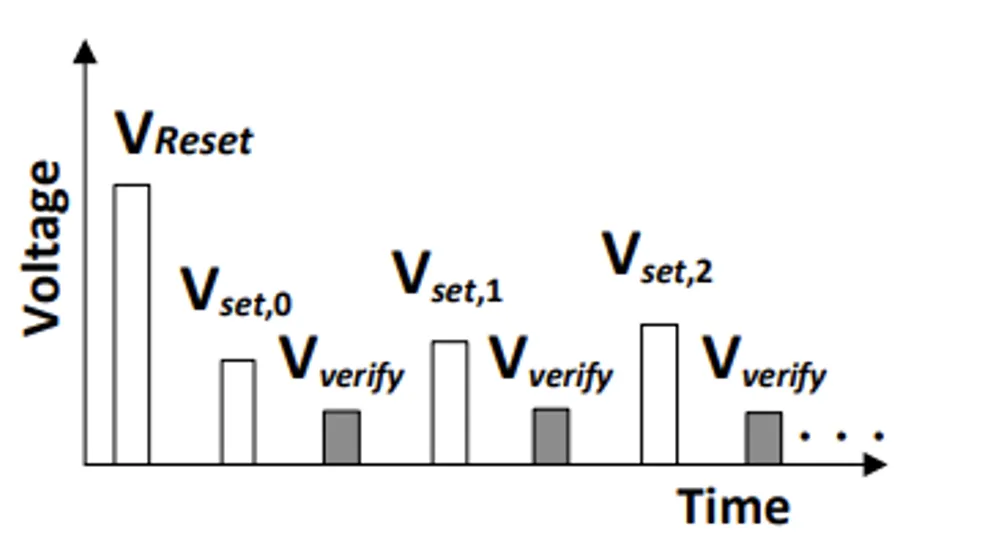

PCM#

PCM实现MLC的方式与Flash类似,也通过 ISPP 编程,通过控制材料的结晶量来区分多个逻辑状态。

写入前先reset,然后通过多次set操作逐步增加结晶量,达到目标状态

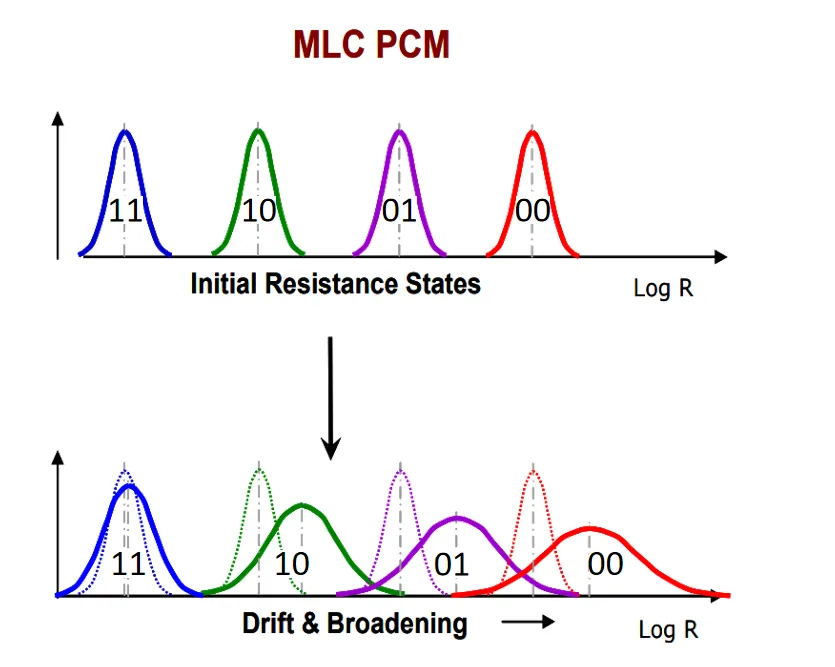

但是PCM实现MLC有独特的挑战:电阻漂移 (Resistance drift)。晶态单元的电阻会随时间逐渐增加,可能导致数据错误

- 晶体的状态是不稳定的,随着时间推移,晶体结构会慢慢变为不定式状态(Amorphous),导致电阻值增加

- 周围其他单元的热干扰也会引起电阻漂移

解决方法:

- 像DRAM一样,定期刷新数据(间隔较长)

NVM Reliability#

NVM 可以在掉电后保存数据,但其存储的信息可能被以下两种因素影响:

- Material-level:由于储存单元自身的原因导致错误

- Array-level:由于阵列结构中其他单元的影响导致错误

Material-level#

Flash

Insulator trap 问题:由于Insulator的老化,电子可能嵌入到Insulator中,导致读取时电阻状态错误

PCM

在高温下,随着时间变化,PCM可能从不定式(Amorphous)状态变为结晶化(Crystalline)状态,导致数据错误

Array-level#

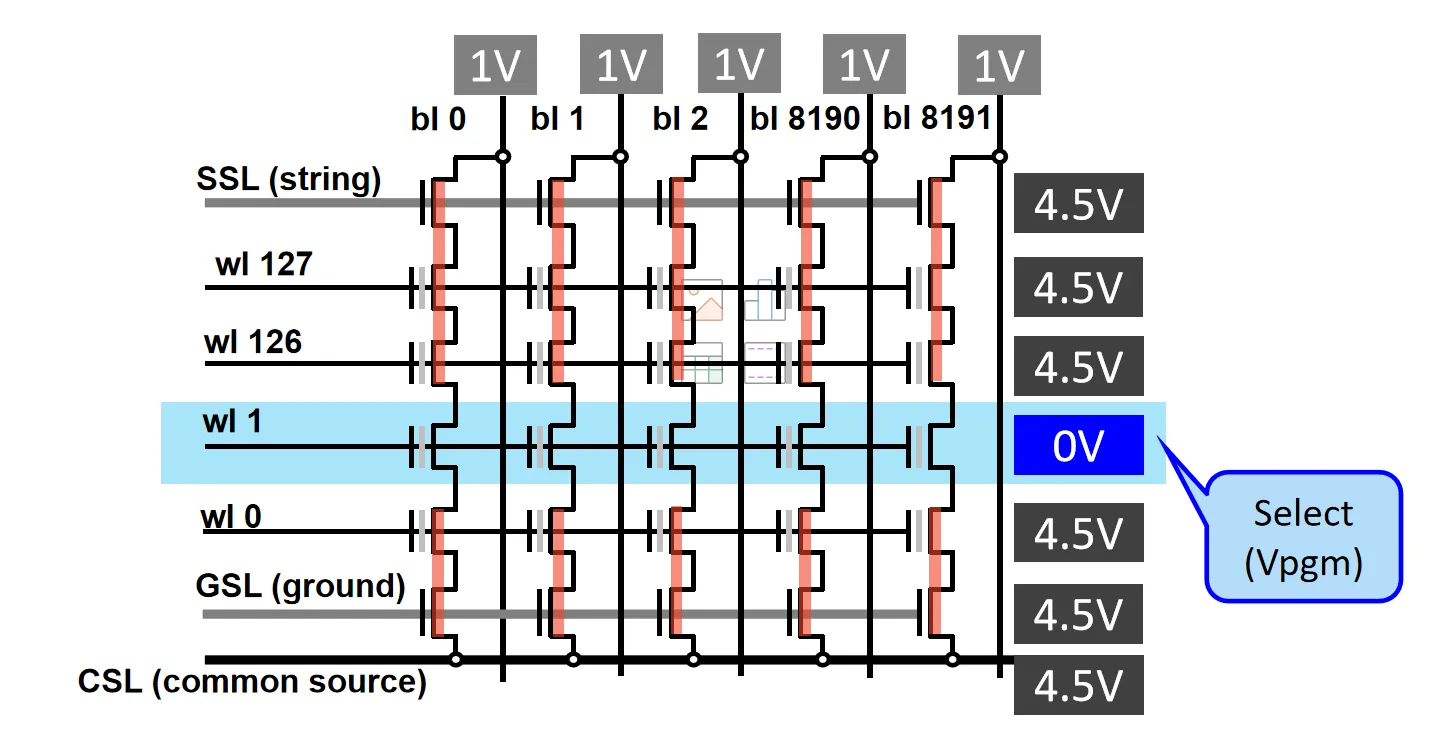

Read Disturbance

正常读取时,未被读取的单元的Control Gate被拉到Vpass电压,选取的单元的Control Gate被拉到0V,然后根据source和drain之间的电流判断电阻状态,读取数据

但是VPass电压虽然不高,仍可能会导致部分电子进入未被读取的单元的FG,导致数据错误,这种情况在 TLC 中更为严重

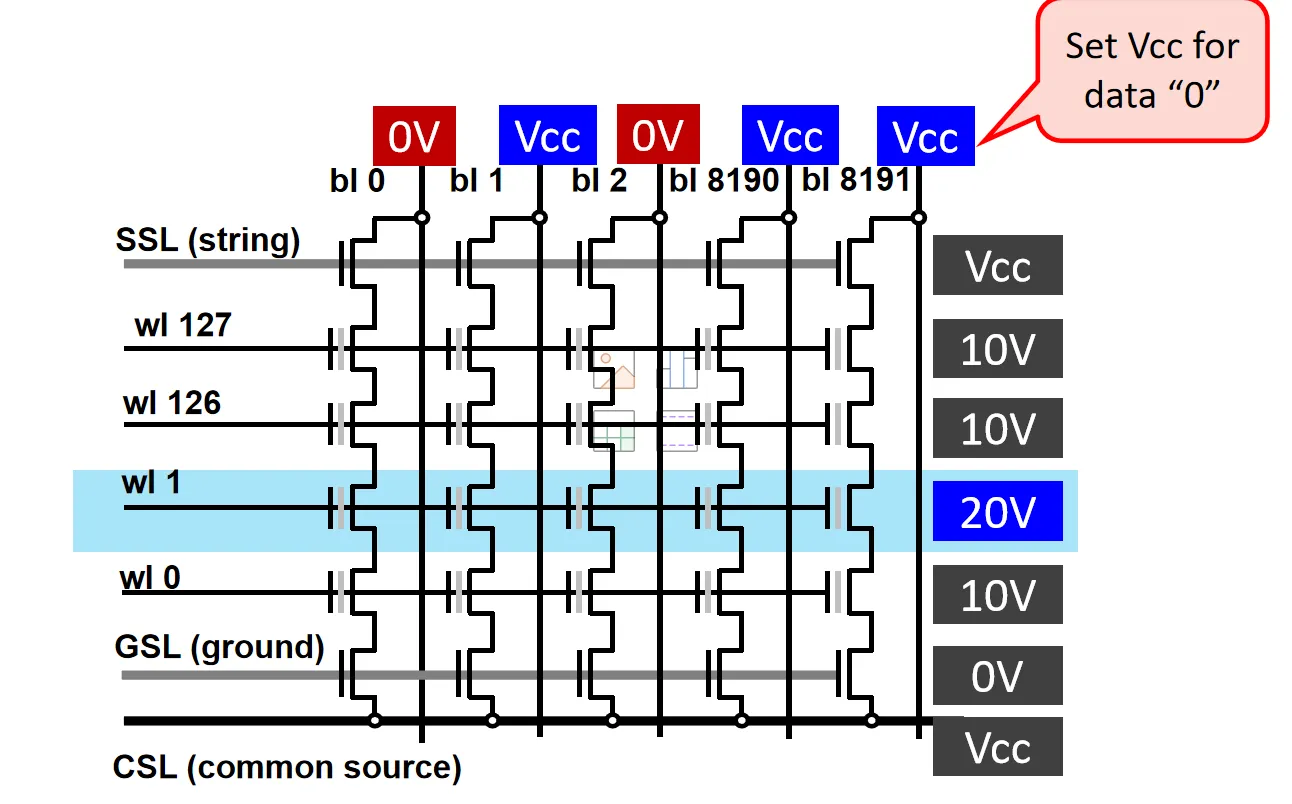

Program Disturbance

写入时,未被写入的单元的Control Gate被拉到Vpass电压,选取的单元的Control Gate被拉到高电压(20V)

由于NAND Flash中多个单元共享bit line,写入时通过bit line注入电子,可能会导致未被写入的单元的FG上也注入电子,导致数据错误。

这个问题比Read Disturbance更严重,因为写入时电压更高,注入的电子更多

解决方法:

蛇形方式写入,对于 TLC

- 第一次写 0,1页

- 第二次写 2,3页的LSB

- 第三次写 4,5页的LSB和2,3页的CSB

- 第四次写 6,7页的LSB;4,5页的CSB;2,3页的MSB……

后一次写入能修改前一次写入可能引起的错误,尽可能减少影响

Array-level Erase#

Flash的擦除

在基座上加上22V的电压,会导致整个block的单元都被擦除,即Erase的规模远大于Program

因此Flash具有Erase-before-Write的特性:在写入数据前,必须先擦除所在的block